# **MP6527**

# 40V, 0.8A, 10-Channel, Half-Bridge Motor Driver with Serial Input Control

### DESCRIPTION

The MP6527 is a ten-channel, half-bridge DMOS output driver with integrated power MOSFETs. It can achieve up to 0.8A of output current ( $I_{OUT}$ ) across a wide 5.5V to 40V input voltage ( $V_{IN}$ ) range from.

The device's ten half-bridges can be controlled separately via a standard serial data interface, and each channel has various diagnostic functions. The MP6527 has very low quiescent current ( $I_Q$ ) in standby mode.

Full protection features include short-circuit protection (SCP), over-temperature protection (OTP), under-voltage lockout (UVLO) protection, over-voltage lockout (OVLO) protection, and thermal shutdown with pre-warning.

The MP6527 requires a minimal number of readily available, standard external components, and is available in a TSSOP-28EP package.

### **FEATURES**

- Wide 5.5V to 40V Operating Input Voltage (V<sub>IN</sub>) Range

- High-Side MOSFETs (HS-FETs) and Low-Side MOSFETs (LS-FETs) Connected in Half-Bridge Configurations

- Up to 0.8A Output Current (I<sub>OUT</sub>)

- Typical 1.3Ω HS-FET and LS-FET R<sub>DS(ON)</sub>

- Low Quiescent Current (I<sub>Q</sub>) in Standby Mode

- Short-Circuit Protection (SCP)

- Over-Temperature Protection (OTP)

- Under-Voltage Lockout (UVLO) and Over-Voltage Lockout (OVLO) Protection

- Serial Data Interface

- Diagnostic Functions:

- Shorted Output

- o Open-Load Detection

- Over-Temperature (OT)

- Over-Voltage (OV)

- Under-Voltage (UV)

- Up to 5MHz Serial Interface Clock Frequency

- Compliance with 3.3V and 5V Systems

- Available in a TSSOP-28EP Package

### **APPLICATIONS**

- Automotive and Industrial Applications

- DC Motors

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

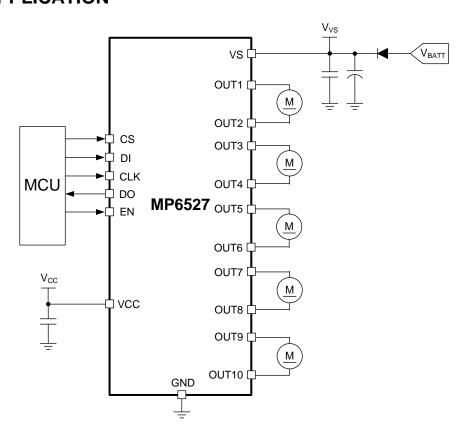

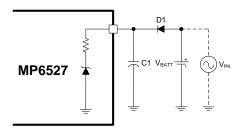

# **TYPICAL APPLICATION**

## ORDERING INFORMATION

| Part Number* | Package    | Top Marking | MSL Rating |

|--------------|------------|-------------|------------|

| MP6527GF     | TSSOP-28EP | See Below   | 2A         |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MP6527GF-Z).

# **TOP MARKING**

# M<u>PSYYWW</u> MP6527 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP6527: Part number LLLLLLLL: Lot number

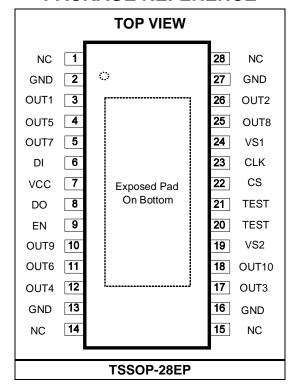

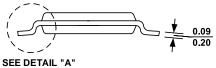

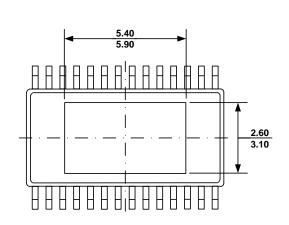

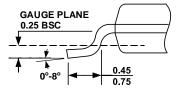

## PACKAGE REFERENCE

# **PIN FUNCTIONS**

| Pin #            | Name  | Description                                                                                      |

|------------------|-------|--------------------------------------------------------------------------------------------------|

| 1, 14,<br>15, 28 | NC    | No connection.                                                                                   |

| 2, 13,<br>16, 27 | GND   | Ground.                                                                                          |

| 3                | OUT1  | Half-bridge output 1.                                                                            |

| 4                | OUT5  | Half-bridge output 5.                                                                            |

| 5                | OUT7  | Half-bridge output 7.                                                                            |

| 6                | DI    | Serial data input.                                                                               |

| 7                | VCC   | Logic supply voltage.                                                                            |

| 8                | DO    | Serial data output.                                                                              |

| 9                | EN    | <b>Enable (EN).</b> Pull the EN pin low for standby mode; pull EN high for normal operation.     |

| 10               | OUT9  | Half-bridge output 9.                                                                            |

| 11               | OUT6  | Half-bridge output 6.                                                                            |

| 12               | OUT4  | Half-bridge output 4.                                                                            |

| 17               | OUT3  | Half-bridge output 3.                                                                            |

| 18               | OUT10 | Half-bridge output 10.                                                                           |

| 19               | VS2   | <b>Power supply for drivers 3, 4, 6, 9 and 10.</b> This pin must be connected to VS1 externally. |

| 20, 21           | TEST  | Internal test pin. Connect the TEST pin to GND.                                                  |

| 22               | CS    | Chip select input, active low.                                                                   |

| 23               | CLK   | Serial clock input.                                                                              |

| 24               | VS1   | Power supply for drivers 1, 2, 5, 7, and 8; the internal LDO; and the charge pump. This          |

|                  |       | pin must be connected to VS2 externally.                                                         |

| 25               | OUT8  | Half-bridge output 8.                                                                            |

| 26               | OUT2  | Half-bridge output 2.                                                                            |

| ABSOLUTE MAXIMUM RATINGS (1)                            |

|---------------------------------------------------------|

| Supply voltage (V <sub>VS</sub> )45V                    |

| V <sub>OUTx</sub> 0.3V to V <sub>IN</sub> +0.3V         |

| Logic supply voltage (V <sub>VCC</sub> )0.3V to +6V     |

| Logic input voltage0.3 to $V_{VCC}$ + 0.3 $V$           |

| Logic output voltage0.3 to $V_{VCC}$ + 0.3 $V$          |

| All other pins0.3V to +6.5V                             |

| Continuous power dissipation ( $T_A = +25$ °C) (2)      |

| TSSOP-28EP                                              |

| Junction temperature                                    |

| Lead temperature260°C                                   |

| Storage temperature65°C to +150°C                       |

| ESD Ratings (3)                                         |

| Human body model (OUTx and VS pins)4kV                  |

| Human body model (all other pins)2kV                    |

| Machine mode (MM)200V                                   |

| Charge device model ( CDM )750V                         |

| Recommended Operating Conditions (4)                    |

| Supply voltage (V <sub>VS</sub> ) 5.5V to 40V           |

| Logic supply voltage V <sub>VCC</sub> 3.15V to 5.25V    |

| Operating junction temp (T <sub>J</sub> )40°C to +125°C |

| Thermal Resistance (5) | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}_{JC}$ |       |

|------------------------|-------------------------|----------------------------|-------|

| TSSOP-28EP             | . 32                    | 6                          | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{\rm J}$  (MAX), the junction-to-ambient thermal resistance  $\theta_{\rm JA}$ , and the ambient temperature  $T_{\rm A}.$  The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{\rm D}$  (MAX) =  $(T_{\rm J}$  (MAX)  $T_{\rm A})$  /  $\theta_{\rm JA}.$  Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- Devices are ESD-sensitive. It is recommended to use extra caution when handling.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$5.5V \le V_{VS} \le 40V$ ,  $3.15V \le V_{VCC} \le 5.25V$ , EN =  $V_{VCC}$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameters                        | Symbol               | Condition                                                                | Min | Тур | Max  | Units |

|-----------------------------------|----------------------|--------------------------------------------------------------------------|-----|-----|------|-------|

| VS supply current                 | lvs                  | Vvs < 28V, EN = Vcc, no load                                             |     | 5.5 | 6.5  | mA    |

|                                   | _                    | 3.15V < V <sub>VCC</sub> < 5.25V, EN = high,                             |     |     |      |       |

| VCC supply current                | Ivcc                 | DI = CLK = low, CS = high, no load                                       |     | 100 | 150  | μA    |

| VS quiescent current              | I <sub>Q_VS</sub>    | Vvs = 13.2V, Vvcc = 0V or Vvcc = 5V,<br>EN = low                         |     | 1   | 5    | μA    |

| VCC quiescent current             | I <sub>Q_</sub> vcc  | 3.15V < V <sub>VCC</sub> < 5.25V, EN = low,<br>DI = CLK = low, CS = high |     | 1   | 5    | μA    |

| VS discharge current              | I <sub>VS</sub> _    | V <sub>VS</sub> = 40V, EN = low                                          |     |     | 3    | mA    |

| Start-up reset threshold          | Vvcc                 | VCC increasing                                                           | 2.3 | 2.7 | 3    | V     |

| Start-up reset delay              |                      | After switching on V <sub>VCC</sub>                                      | 30  | 100 | 160  | μs    |

| VS under-voltage lockout          | V <sub>UVLO_VS</sub> | VS decreasing                                                            | 3.5 |     | 4.5  | V     |

| (UVLO) threshold                  | V UVLO_VS            | v3 decreasing                                                            | 5.5 |     | 4.5  | V     |

| VS UVLO threshold                 | $V_{UVOFF}$          |                                                                          | 0.1 | 0.3 | 0.5  | V     |

| hysteresis                        | VUVOFF               |                                                                          |     | 0.0 |      | v     |

| VS UVLO delay time                |                      |                                                                          | 7   |     | 21   | ms    |

| VS over-voltage lockout           | Vovio ve             | OVLO = 1, VS increasing                                                  | 33  | 36  | 39   | V     |

| (OVLO) threshold                  | VOVLO_VS             | Over 1, vo moreasing                                                     |     | 00  | - 00 | v     |

| VS OVLO threshold                 |                      |                                                                          | 1   | 2.5 | 4    | V     |

| hysteresis                        |                      |                                                                          | •   |     | •    | ·     |

| Output Specifications             |                      |                                                                          |     | Т   | 1    | 1     |

| HS-FET and LS-FET on              | R <sub>DS(ON)</sub>  |                                                                          |     | 1.3 | 1.6  | Ω     |

| resistance                        |                      |                                                                          |     |     |      | 32    |

| Over-current (OC) limit           | I <sub>OCP</sub>     | V <sub>VS</sub> = 13.2V                                                  | 11  | 1.3 | 2.5  | Α     |

| OC shutdown delay time            | t <sub>dOC</sub>     | V V3 = 10.2 V                                                            | 10  | 25  | 50   | μs    |

| Open-load detection (OLD) current | I <sub>OLD</sub>     | V <sub>VS</sub> = 13.2V, LS-FET is on                                    | 1   | 16  | 45   | mA    |

| OLD delay time                    | tDELAY_OLD           |                                                                          | 200 | 350 | 600  | μs    |

| Output enable time                |                      | V 12 2V B = 500                                                          |     | 50  | 65   |       |

| Output disable time               |                      | $V_{VS} = 13.2V$ , $R_{LOAD} = 50\Omega$                                 |     | 50  | 65   |       |

| Delay time                        |                      | HBCNFx high to OUTx high,<br>$V_{VS} = 13.2V$ , $R_{LOAD} = 50Ω$         |     | 75  | 105  | μs    |

| Delay time                        |                      | HBCNFx low to OUTx low,<br>$V_{VS} = 13.2V$ , $R_{LOAD} = 50Ω$           |     | 65  | 95   |       |

| Output rise time                  |                      | $V_{VS}$ = 13.2V, 10% to 90% $V_{OUT}$ , $R_{LOAD}$ = 50 $\Omega$        | 13  | 27  | 42   | μs    |

| Output fall time                  |                      |                                                                          | 11  | 20  | 27   | μs    |

| Dead time                         |                      | $V_{VS} = 13V$ , $R_{LOAD} = 50\Omega$                                   | 1.5 |     |      | μs    |

| Enable (EN) Input                 |                      |                                                                          |     |     |      |       |

| EN low threshold                  |                      |                                                                          |     |     | 0.6  | V     |

| EN high threshold                 |                      |                                                                          | 2   |     |      | V     |

| EN threshold hysteresis           |                      |                                                                          |     | 0.4 |      | V     |

| Pull-down resistor                |                      | V <sub>EN</sub> = V <sub>VCC</sub>                                       |     | 125 |      | kΩ    |

| Serial Interface: Logic In        | outs (DI, C          |                                                                          |     |     |      |       |

| Input low-level threshold         |                      |                                                                          |     |     | 0.6  | V     |

| Input high-level threshold        |                      |                                                                          | 2   |     |      | V     |

| Input threshold hysteresis        |                      |                                                                          |     | 150 |      | mV    |

| DI pull-down resistor,            |                      | V V                                                                      |     |     |      |       |

| CLK pin                           |                      | $V_{DI}, V_{CLK} = V_{VCC}$                                              |     | 125 |      | kΩ    |

| CS pull-up current                |                      | Vcs = 0V                                                                 |     | 125 |      | kΩ    |

| Input capacitance (6)             | Cin                  |                                                                          |     |     | 15   | pF    |

# **ELECTRICAL CHARACTERISTICS** (continued)

$5.5V \le V_{VS} \le 40V$ ,  $3.15V \le V_{VCC} \le 5.25V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                         | Symbol                | Condition                                             | Min                    | Тур | Max | Units |

|----------------------------------------------------|-----------------------|-------------------------------------------------------|------------------------|-----|-----|-------|

| Serial Interface: Logic Output (DO)                |                       |                                                       |                        |     |     |       |

| Output low level                                   |                       |                                                       |                        |     | 0.4 | V     |

| Output high level                                  |                       |                                                       | V <sub>VCC</sub> - 0.6 |     |     | V     |

| Leakage current (tri-state)                        |                       | $0V < V_{DO} < V_{VCC}, V_{CS} = V_{VCC}$             | -5                     |     | +5  | μA    |

| Thermal Shutdown and Pre-                          | Warning               | (6)                                                   |                        |     |     |       |

| Thermal pre-warning                                | T <sub>JW</sub>       |                                                       | 120                    | 140 | 170 | °C    |

| threshold                                          | I JVV                 |                                                       | 120                    | 140 | 170 | C     |

| Thermal pre-warning                                |                       |                                                       |                        | 20  |     | °C    |

| hysteresis                                         |                       |                                                       |                        | 20  |     | _     |

| Thermal shutdown threshold                         | T <sub>JSD</sub>      |                                                       | 150                    | 175 | 200 | °C    |

| Thermal shutdown hysteresis                        |                       |                                                       |                        | 20  |     | °C    |

| Ratio for thermal shutdown                         |                       |                                                       | 1.05                   | 1.2 |     |       |

| and thermal pre-warning                            |                       |                                                       | 1.05                   | 1.2 |     |       |

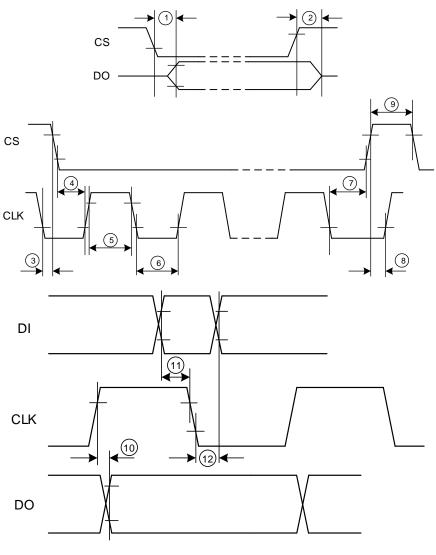

| CLK frequency                                      | fclk                  |                                                       |                        |     | 5   | MHz   |

| CLK period time                                    | tpclk                 | $V_{CC} = 5V$                                         | 200                    |     |     | ns    |

| •                                                  | IPCLK                 | $V_{CC} = 3.3V$                                       | 500                    |     |     |       |

| CLK high time                                      | <b>t</b> 5            |                                                       | 85                     |     |     | ns    |

| CLK low time                                       | t <sub>6</sub>        |                                                       | 85                     |     |     | ns    |

| CLK set-up time (high to low)                      | t <sub>7</sub>        |                                                       | 85                     |     |     | ns    |

| CLK set-up time (low to high)                      | <b>t</b> <sub>3</sub> |                                                       | 85                     |     |     | ns    |

| DI set-up time                                     | t <sub>11</sub>       |                                                       | 50                     |     |     | ns    |

| DI hold time                                       | t <sub>12</sub>       |                                                       | 50                     |     |     | ns    |

| CS set-up time (low to high)                       | t <sub>8</sub>        |                                                       | 100                    |     |     | ns    |

| CS set-up time (high to low)                       | t <sub>4</sub>        |                                                       | 100                    |     |     | ns    |

| CS high time                                       | <b>t</b> 9            |                                                       | 5                      |     |     | μs    |

| DO enable after CS falling                         | t <sub>1</sub>        | C <sub>DO</sub> = 40pF                                |                        |     | 200 | ns    |

| edge                                               | l1                    | CD0 = 40pF                                            |                        |     | 200 | 115   |

| DO disable after CS rising                         | t <sub>2</sub>        | C <sub>DO</sub> = 40pF                                |                        |     | 200 | ns    |

| edge                                               | t <sub>2</sub>        | ·                                                     |                        |     | 200 | 115   |

| DO fall/rise time                                  |                       | C <sub>DO</sub> = 40pF                                |                        | 10  | 25  | ns    |

| DO valid time                                      | t <sub>10</sub>       | C <sub>DO</sub> = 40pF                                |                        | 20  | 50  | ns    |

| EN low valid time                                  |                       | Vcc = 5V, EN high to low, 50% to OUTx turning off 50% |                        | 50  |     | μs    |

| EN high to serial peripheral interface (SPI) valid |                       |                                                       |                        |     | 100 | μs    |

| Time between two consecutive SRR commands          |                       |                                                       | 100                    |     |     | ms    |

#### Note:

6) Not subject to production testing. Guaranteed by design.

7

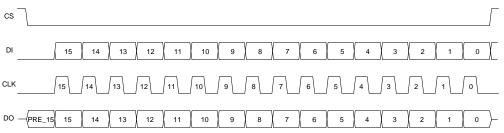

Inputs DI, CLK, CS: High Level = 0.7 x V $_{\rm CC}$ , Low Level = 0.3 x V $_{\rm CC}$  Output DO: High Level = 0.8 x V $_{\rm CC}$ , Low Level = 0.2 x V $_{\rm CC}$

Figure 1: Serial Interface Timing Diagram

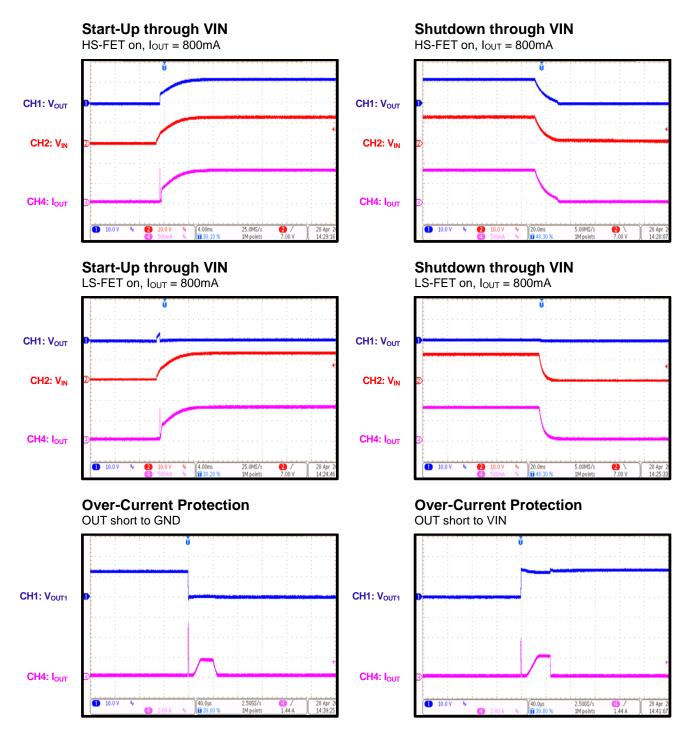

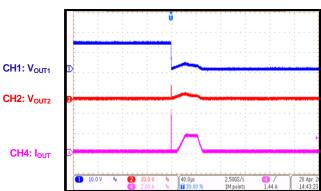

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{VS}$  = 13V,  $V_{VCC}$  = 3.3V,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{VS}$  = 13V,  $V_{VCC}$  = 3.3V,  $T_A$  = 25°C, unless otherwise noted.

## **OCP**

OUT short to OUT

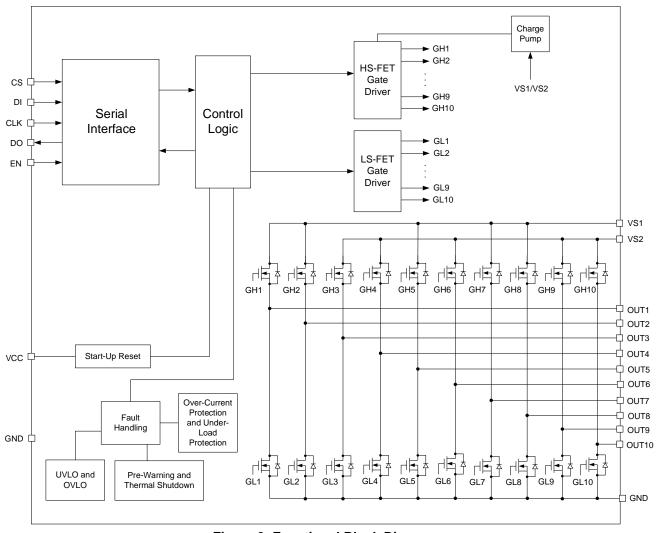

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

### **OPERATION**

The MP6527 is a 10-channel, half-bridge double-DMOS output driver with integrated power MOSFETs. The IC's 10 half-bridges can be controlled separately via a standard serial data interface, and have various diagnostic functions.

#### **Serial Interface**

Data transfer starts with the falling edge signal of the CS pin. Execution of new input data is enabled on the rising edge of the CS signal. Data must appear at the DI pin synchronized to the CLK pin, and is accepted on the falling edge of the CLK signal. For DI, the MSB (SRR, bit[15]) must be transferred first. The last 16 bits clocked into DI are transferred to the device's data register if there is no frame error. Otherwise, all DI data is ignored and the previous input data is preserved.

The output data at the DO pin is enabled on the falling edge of CS. In addition to the 16-bit status

data, a pseudo-bit (PRE\_15) can also be retrieved from the DO output. The latched thermal shutdown (TSD) status bit (PRE\_15) is available on DO until the first rising CLK edge after CS goes low. The output data changes their state with the CLK rising edge, and remains stable until the next CLK rising edge appears. When CS is high, DO is in a tri-state condition.

The following conditions must be met for a valid TSD read to be captured:

- 1. CLK and DI are low before the CS cycle begins.

- 2. CS transitions from high to low.

- 3. The CS set-up time is satisfied.

Figure 3 shows the SPI communication. Table 1 and Table 2 show the input control registers. Table 3 and Table 4 show the output diagnostic registers.

Figure 3: Data Transfer

Table 1: Input Control Registers (Channels 1 to 6, Input Bit[14] = 0)

|     | Channels 1 to 6 (Input Bit[14] = 0) |                                                                                                                                                                                                                             |  |  |

|-----|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Input Register                      | Function                                                                                                                                                                                                                    |  |  |

|     |                                     | Status register reset.                                                                                                                                                                                                      |  |  |

| 15  | SRR                                 | 1: Reset, the error bits of the corresponding status register in the output data register are set to low 0: Not reset, SRR is invalid                                                                                       |  |  |

|     |                                     | This bit selects the channel group.                                                                                                                                                                                         |  |  |

| 14  | CH_SEL                              | 1: Half-bridge, bits[10:7]<br>0: Half-bridge, bits [6:1]                                                                                                                                                                    |  |  |

| 13  | OLSD_EN                             | This bit enables open-load detection shutdown (OLD_SD) for half-bridge 1 (HB1) to half-bridge 6 (HB6). This feature allows the affected output stage to switch off if a true open-load or under-load condition is detected. |  |  |

|     |                                     | 1: Enabled<br>0: Disabled                                                                                                                                                                                                   |  |  |

|     |                                     | Enables half-bridge 6.                                                                                                                                                                                                      |  |  |

| 12  | HBEN6                               | 1: Half-bridge 6 is active<br>0: Half-bridge 6 is in Hi-Z                                                                                                                                                                   |  |  |

|    | T      |                                                                                                                                            |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

|    |        | Enables half-bridge 5.                                                                                                                     |

| 11 | HBEN5  | 1: Half-bridge 5 is active 0: Half-bridge 5 is in Hi-Z                                                                                     |

|    |        | Enables half-bridge 4.                                                                                                                     |

| 10 | HBEN4  | 1: Half-bridge 4 is active 0: Half-bridge 4 is in Hi-Z                                                                                     |

|    |        | Enables half-bridge 3.                                                                                                                     |

| 9  | HBEN3  | 1: Half-bridge 3 is active 0: Half-bridge 3 is in Hi-Z                                                                                     |

|    |        | Enables half-bridge 2.                                                                                                                     |

| 8  | HBEN2  | 1: Half-bridge 2 is active 0: Half-bridge 2 is in Hi-Z                                                                                     |

|    |        | Enables half-bridge 1.                                                                                                                     |

| 7  | HBEN1  | 1: Half-bridge 1 is active 0: Half-bridge 1 is in Hi-Z                                                                                     |

|    |        | Configures half-bridge 6.                                                                                                                  |

| 6  | HBCNF6 | 1: The high-side (HS) half-bridge is on and the low-side (LS) half-bridge is off 0: The HS half-bridge is off and the LS half-bridge is on |

|    |        | Configures half-bridge 5.                                                                                                                  |

| 5  | HBCNF5 | 1: The HS half-bridge is on and the LS half-bridge is off 0: The HS half-bridge is off and the LS half-bridge is on                        |

|    |        | Configures half-bridge 4.                                                                                                                  |

| 4  | HBCNF4 | 1: The HS half-bridge is on and the LS half-bridge is off 0: The HS half-bridge is off and the LS half-bridge is on                        |

|    |        | Configures half-bridge 3.                                                                                                                  |

| 3  | HBCNF3 | 1: The HS half-bridge is on and the LS half-bridge is off 0: The HS half-bridge is off and the LS half-bridge is on                        |

|    |        | Configures half-bridge 2.                                                                                                                  |

| 2  | HBCNF2 | 1: The HS half-bridge is on and the LS half-bridge is off 0: The HS half-bridge is off and the LS half-bridge is on                        |

|    |        | Configures half-bridge 1.                                                                                                                  |

| 1  | HBCNF1 | 1: The HS half-bridge is on and the LS half-bridge is off 0: The HS half-bridge is off and the LS half-bridge is on                        |

|    |        | Enables VSx over-voltage lockout (OVLO).                                                                                                   |

| 0  | OVLO   | 1: Enabled 0: Disabled                                                                                                                     |

# Table 2: Input Control Registers (Channels 7 to 10, Input Bit[14] = 1)

|     | Channels 7 to 10 (Input Bit[14] = 1) |                                                                                                                                                                                                                               |  |  |

|-----|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Input Register                       | Function                                                                                                                                                                                                                      |  |  |

|     |                                      | Status register reset.                                                                                                                                                                                                        |  |  |

| 15  | SRR                                  | Reset, the error bits of the corresponding status register in the output data register are set to low     Not reset, SRR is invalid                                                                                           |  |  |

|     |                                      | This bit selects the channel group.                                                                                                                                                                                           |  |  |

| 14  | CH_SEL                               | 1: Half-bridge, bits[10:7]<br>0: Half-bridge, bits[6:1]                                                                                                                                                                       |  |  |

| 13  | OLSD_EN                              | This bit enables open-load detection shutdown (OLD_SD) for half-bridge 7 (HB7) to half-bridge 10 (HB10). This feature allows the affected output stage to switch off if a true open-load or under-load condition is detected. |  |  |

|     |                                      | 1: Enabled<br>0: Disabled                                                                                                                                                                                                     |  |  |

| 12  | RESERVED                             | Not used.                                                                                                                                                                                                                     |  |  |

| 11  | RESERVED                             | Not used.                                                                                                                                                                                                                     |  |  |

|     |                                      | Enables half-bridge 10.                                                                                                                                                                                                       |  |  |

| 10  | HBEN10                               | 1: Half-bridge 10 is active<br>0: Half-bridge 10 is in Hi-Z                                                                                                                                                                   |  |  |

|     |                                      | Enables half-bridge 9.                                                                                                                                                                                                        |  |  |

| 9   | HBEN9                                | 1: Half-bridge 9 is active<br>0: Half-bridge 9 is in Hi-Z                                                                                                                                                                     |  |  |

|     |                                      | Enables half-bridge 8.                                                                                                                                                                                                        |  |  |

| 8   | HBEN8                                | 1: Half-bridge 8 is active<br>0: Half-bridge 8 is in Hi-Z                                                                                                                                                                     |  |  |

|     |                                      | Enables half-bridge 7.                                                                                                                                                                                                        |  |  |

| 7   | HBEN7                                | 1: Half-bridge 7 is active<br>0: Half-bridge 7 is in Hi-Z                                                                                                                                                                     |  |  |

| 6   | RESERVED                             | Not used.                                                                                                                                                                                                                     |  |  |

| 5   | RESERVED                             | Not used.                                                                                                                                                                                                                     |  |  |

|     |                                      | Configures half-bridge 10.                                                                                                                                                                                                    |  |  |

| 4   | HBCNF10                              | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                        |  |  |

|     |                                      | Configures half-bridge 9.                                                                                                                                                                                                     |  |  |

| 3   | HBCNF9                               | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                        |  |  |

|     |                                      | Configures half-bridge 8.                                                                                                                                                                                                     |  |  |

| 2   | HBCNF8                               | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                        |  |  |

|   |        | Configures half-bridge 7.                                 |

|---|--------|-----------------------------------------------------------|

| 1 | HBCNF7 | 1: The HS half-bridge is on and the LS half-bridge is off |

|   |        | 0: The HS half-bridge is off and the LS half-bridge is on |

|   |        | Enables VSx OVLO.                                         |

| 0 | OVLO   | 1: Enabled<br>0: Disabled                                 |

#### Note:

Table 3: Output Diagnostic Registers (Channels 1 to 6, Input Bit[14] = 0)

|        | Channels 1 to 6 (Input Bit[14] = 0) |                                                                                                                                                                                                                                                                                |  |  |

|--------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit    | Input Register                      | Function                                                                                                                                                                                                                                                                       |  |  |

| PRE_15 | TSD                                 | Latched thermal shutdown (TSD). This bit is latched, and the corresponding output is switched off. This bit can only be reset via status register reset (SRR) or a power-on reset.                                                                                             |  |  |

|        |                                     | 1: Fault<br>0: No fault                                                                                                                                                                                                                                                        |  |  |

| 15     | OC<br>(HB [6:1])                    | Latched over-current (OC) shutdown. This bit is set and latched if a half-bridge from HB1 to HB6 has an overload or short-circuit. The corresponding output is also switched off. This bit can only be reset via SRR or a power-on reset.                                      |  |  |

|        | (116 [0.1])                         | 1: Fault<br>0: No fault                                                                                                                                                                                                                                                        |  |  |

| 14     | PSF                                 | Power supply failure. This bit is set and latched if a VS1, VS2, or VS1 and VS2 over-voltage (OV) or under-voltage (UV) conditions occurs. All outputs are switched off. This bit resets automatically if VSx returns to its normal operating range.                           |  |  |

|        |                                     | 1: Fault<br>0: No fault                                                                                                                                                                                                                                                        |  |  |

| 13     | OLD<br>(HB [6:1])                   | Open-load error. This bit is set and latched if a half-bridge from HB1 to HB6 experiences an open-load or under-load error condition. The corresponding output is also switched off if input bit[13] (OLD_SD) is high. This bit can only be reset via SRR or a power-on reset. |  |  |

|        |                                     | 1: Fault<br>0: No fault                                                                                                                                                                                                                                                        |  |  |

|        |                                     | Returns half-bridge 6's output status.                                                                                                                                                                                                                                         |  |  |

| 12     | SHBEN6                              | 1: HB6 is active<br>0: HB6 is in Hi-Z                                                                                                                                                                                                                                          |  |  |

|        |                                     | Returns half-bridge 5's output status.                                                                                                                                                                                                                                         |  |  |

| 11     | SHBEN5                              | 1: HB5 is active<br>0: HB5 is in Hi-Z                                                                                                                                                                                                                                          |  |  |

|        |                                     | Returns half-bridge 4's output status.                                                                                                                                                                                                                                         |  |  |

| 10     | SHBEN4                              | 1: HB4 is active<br>0: HB4 is in Hi-Z                                                                                                                                                                                                                                          |  |  |

<sup>7)</sup> All input bits are set to 0 after  $V_{\text{CC}}$  power-on reset.

|   |        | Returns half-bridge 3's output status.                                                                                                                                                                                                                                                    |

|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9 | SHBEN3 | 1: HB3 is active 0: HB3 is in Hi-Z                                                                                                                                                                                                                                                        |

|   |        | Returns half-bridge 2's output status.                                                                                                                                                                                                                                                    |

| 8 | SHBEN2 | 1: HB2 is active                                                                                                                                                                                                                                                                          |

|   |        | 0: HB2 is in Hi-Z                                                                                                                                                                                                                                                                         |

|   |        | Returns half-bridge 1's output status.                                                                                                                                                                                                                                                    |

| 7 | SHBEN1 | 1: HB1 is active<br>0: HB1 is in Hi-Z                                                                                                                                                                                                                                                     |

|   |        | Returns half-bridge 6's configuration status.                                                                                                                                                                                                                                             |

| 6 | HBCNF6 | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                                                    |

|   |        | Returns half-bridge 5's configuration status.                                                                                                                                                                                                                                             |

| 5 | HBCNF5 | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                                                    |

|   |        | Returns half-bridge 4's configuration status.                                                                                                                                                                                                                                             |

| 4 | HBCNF4 | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                                                    |

|   |        | Returns half-bridge 3's configuration status.                                                                                                                                                                                                                                             |

| 3 | HBCNF3 | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                                                    |

|   |        | Returns half-bridge 2's configuration status.                                                                                                                                                                                                                                             |

| 2 | HBCNF2 | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                                                    |

|   |        | Returns half-bridge 1's configuration status.                                                                                                                                                                                                                                             |

| 1 | HBCNF1 | 1: The HS half-bridge is on and the LS half-bridge is off<br>0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                                                    |

| 0 | TW     | Thermal warning. This bit is treated as a pre-warning to TSD, and goes high if the junction temperature reaches TJW. The output remains on until one or more sensors reach TSD. This bit automatically resets if the junction temperature drops below the thermal warning recovery point. |

|   |        | 1: Fault<br>0: No fault                                                                                                                                                                                                                                                                   |

## Table 4: Output Diagnostic Registers (Channels 7 to 10, Input Bit[14] = 1)

| Channels 7 to 10 (Input Bit[14] = 1) |                |                                                                                                                                                                                          |  |  |  |  |

|--------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit                                  | Input Register | Function                                                                                                                                                                                 |  |  |  |  |

| PRE_15                               | TSD            | Latched thermal shutdown (TSD). This bit is set and latched, and the corresponding output is switched off. This bit can only be reset via SRR or a power-on reset.  1: Fault 0: No fault |  |  |  |  |

| 15     | OC<br>(HB [10:7])  | Latched over-current (OC) shutdown. This bit is set and latched if a half-bridge from HB7 to HB10 experiences an overload or short-circuit. The corresponding output is also switched off. This bit can only be reset via SRR or a power-on reset.  1: Fault 0: No fault        |  |  |  |

|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14 PSF |                    | Power supply failure. This bit is set if a VS1, VS2, or VS1 and a VS2 OV or UV condition occurs. All outputs are switched off. This bit resets automatically if VSx returns to within its normal operating range.                                                               |  |  |  |

|        |                    | 1: Fault 0: No fault                                                                                                                                                                                                                                                            |  |  |  |

| 13     | OLD<br>(HB [10:7]) | Open-load error. This bit is set and latched if a half-bridge from HB7 to HB10 experiences an open-load or under-load error condition. The corresponding output is also switched off if input bit[13] (OLD_SD) is high. This bit can only be reset via SRR or a power-on reset. |  |  |  |

|        |                    | 1: Fault<br>0: No fault                                                                                                                                                                                                                                                         |  |  |  |

| 12     | RESERVED           | Not used.                                                                                                                                                                                                                                                                       |  |  |  |

| 11     | RESERVED           | Not used.                                                                                                                                                                                                                                                                       |  |  |  |

| 10     | SHBEN10            | Returns half-bridge 10's output status.  1: Half-bridge 10 is active  0: Half-bridge 10 is in Hi-Z                                                                                                                                                                              |  |  |  |

| 9      | SHBEN9             | Returns half-bridge 9's output status.  1: Half-bridge 9 is active  0: Half-bridge 9 is in Hi-Z                                                                                                                                                                                 |  |  |  |

| 8      | SHBEN8             | Returns half-bridge 8's output status.  1: Half-bridge 8 is active  0: Half-bridge 8 is in Hi-Z                                                                                                                                                                                 |  |  |  |

| 7      | SHBEN7             | Returns half-bridge 7's output status.  1: Half-bridge 7 is active  0: Half-bridge 7 is in Hi-Z                                                                                                                                                                                 |  |  |  |

| 6      | RESERVED           | Not used.                                                                                                                                                                                                                                                                       |  |  |  |

| 5      | RESERVED           | Not used.                                                                                                                                                                                                                                                                       |  |  |  |

| 4      | HBCNF10            | Returns half-bridge 10's configuration status.  1: The HS half-bridge is on and the LS half-bridge is off  0: The HS half-bridge is off and the LS half-bridge is on                                                                                                            |  |  |  |

| 3      | HBCNF9             | Returns half-bridge 9's configuration status.  1: The HS half-bridge is on and the LS half-bridge is off  0: The HS half-bridge is off and the LS half-bridge is on                                                                                                             |  |  |  |

| 2 | HBCNF8 | Returns half-bridge 8's configuration status.  1: The HS half-bridge is on and the LS half-bridge is off  0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                             |

|---|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | HBCNF7 | Returns half-bridge 7's configuration status.  1: The HS half-bridge is on and the LS half-bridge is off  0: The HS half-bridge is off and the LS half-bridge is on                                                                                                                                             |

| 0 | TW     | Thermal warning. This bit is treated as a pre-warning to TSD, and goes high if the junction temperature reaches TJW. The output remains on until one or more sensors reach TSD. This bit automatically resets if the junction temperature drops below the thermal warning recovery point.  1: Fault 0: No fault |

#### **Enable Control**

The MP6527 enters low-power mode (or sleep mode) when the EN pin is set to low. The EN input has an internal pull-down resistor. In sleep mode, all output stages are turned off and the SPI register banks are reset. The output stages can be activated again by setting EN to high.

### **Status Register Reset (SRR)**

The status register reset (SRR) command bit is executed after the SPI transmission determines whether a fault has been cleared.

Sending 1 to SSR clears the status memory and reactivates faulted outputs for channels (as selected by CH\_SEL).

If a fault remains present after SRR, the corresponding protection can be re-engaged and shutdown can recur. The device can also be reset by toggling the EN pin or by a VCC power-on reset.

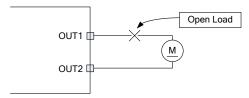

### **Open-Load Detection (OLD)**

When the device is on, open-load detection (OLD) is implemented in the low-side MOSFET (LS-FET) switches of the bridge outputs. If the current through the low-side (LS) transistor is below the reference current (I<sub>OLD</sub>) for longer than the OLD delay time (t<sub>DOLD</sub>), then the corresponding open-load diagnosis bit is set. If an under-load condition occurs in another channel after the global timer has started, the delay for any subsequent under-load condition becomes the remainder of the timer. The timer runs continuously with a persistent under-load condition.

If the OLSD\_EN bit is set and an open load is detected on the LS-FET, the respective output is disabled and the open-load error bit is latched. Otherwise, the output remains on and the open-load error bit is set. The bit remains latched and the output remains off until an SRR or power-on reset is performed. The channel group select (CH\_SEL) input bit determines which channels are affected by SRR and which half-bridges are latched off via the OLSD\_EN command bit. This has the added advantage of independently diagnosing and isolating error flags to the corresponding failed output.

Figure 4 shows an H-bridge open-load example, where a motor is connected between OUT1 and OUT2 with a broken wire.

Figure 4: H-Bridge Open Load Example

Table 5 shows an example of the resulting diagnostic information.

Table 5: Open-Load Diagnostic Example

| Control |     |     |     | Diagnostic<br>Information |                       |  |

|---------|-----|-----|-----|---------------------------|-----------------------|--|

|         |     |     |     | Motor<br>Connected        | Motor<br>Disconnected |  |

| LS1     | HS1 | LS2 | HS2 | OLD (output bit[13])      |                       |  |

| 0       | 0   | 0   | 0   | 0                         | 0                     |  |

| 1       | 0   | 0   | 1   | 0                         | 1                     |  |

| 0       | 1   | 1   | 0   | 0                         | 1                     |  |

| 0       | 1   | 0   | 1   | 0                         | 0                     |  |

| 1       | 0   | 1   | 0   | 1                         | 1                     |  |

In motor applications, it is often desirable to actively brake the motor by turning on both HS drivers or LS drivers in two half-bridge channels. If two LS drivers are used (an LS brake), an under-load condition occurs as the motor current decays normally. It is recommended to use an HS brake instead to avoid the under-load condition.

### **Discharge Circuit**

Many typical applications use an inverse-polarity protection diode. Figure 5 shows the functional principle of a discharger circuit, with an inverse-polarity protection diode (D1).

Figure 5: Functional Principle of a Discharger Circuit

However, this method poses certain risks. During inhibit mode, the IC consumes an extremely low discharge current ( $I_{VS}$ ), typically

$20\mu A$  max. Any peaks on the supply voltage gradually charge the blocking capacitor. D1 prevents the capacitor from discharging via the power supply. Due to the extremely small quiescent current ( $I_Q$ ), discharging via the IC is negligible. During long periods of time in inhibit mode, the IC's supply voltage could increase continuously until the maximum supply voltage limit (40V) is exceeded, which can damage the IC. To avoid this, the MP6527 features a discharge circuit. If the VS pin voltage ( $V_{VS}$ ) exceeds the 37V threshold, the blocking capacitor is discharged via an integrated resistor until  $V_{VS}$  falls below the threshold.

Table 6 shows the diagnostic classes and functions of the different faults.

Table 6: Diagnostic Classes and Functions of Different Faults

|                 |            | State and Recovery                |                                 |  |

|-----------------|------------|-----------------------------------|---------------------------------|--|

| Fault           | Qualifier  | OUTx                              | Output<br>Register              |  |

| TSD             | - n        |                                   | TSD: 1,<br>need SRR<br>to reset |  |

| OC<br>shutdown  | -          | Hi-Z, need<br>SRR to reset        | OC: 1,<br>need SRR<br>to reset  |  |

|                 | OLSD_EN: 1 |                                   | OLD: 1,                         |  |

| OLD             | OLSD_EN: 0 | Unaffected                        | need SRR<br>to reset            |  |

| OVLO            | OVLO: 1    | Hi-Z,<br>Unlatched <sup>(8)</sup> | DCE: 4                          |  |

|                 | OVLO: 0    | Unaffected                        | PSF: 1,<br>unlatched            |  |

| UVLO            | -          | Hi-Z,<br>Unlatched (8)            | (9)                             |  |

| Thermal warning | -          | Unaffected                        | TW: 1,<br>unlatched             |  |

#### Notes:

- OUTx returns to its previous state or new state once the fault is removed. If DI changes, then DO changes accordingly.

- The corresponding output register returns to its no-fault state once the fault is removed.

### **Over-Current Protection (OCP)**

The MP6527 has internal overload protection (OLP) and short-circuit protection (SCP). The currents in both the HS-FET and LS-FET are measured. If the current through the HS-FET or LS-FET exceeds the current limit, an internal timer starts. When a permanent over-current shutdown delay time ( $t_{\rm OC}$ ) is reached, the short-circuit detection bit (OC) is set and the shorted output is disabled. By writing 1 to the SRR bit in the input register, the OC bit resets and the

disabled outputs are enabled. The channel group select (CH\_SEL) input bit determines which channels are affected by SRR.

## Thermal Shutdown (TSD) and Pre-Warning

The MP6572 has integrated thermal monitoring for each half-bridge via the driver pair's thermal sensor. If the junction temperature  $(T_J)$  exceeds the thermal pre-warning threshold, then the temperature pre-warning bit (TW) in the output register is set. When the temperature falls below the thermal pre-warning threshold, TW is reset.

If  $T_J$  exceeds the thermal shutdown (TSD) threshold, then the channel's HS-FETs and LS-FETs are latched off, TW remains set, and the TSD bit (PRE\_15) is set. Once  $T_J$  falls below the TSD threshold and a high has been written to the SRR bit in the input register, then TSD is cleared and all the affected channels in a group resume normal operation. The channel group select (CH\_SEL) input bit determines which channels are affected by SRR.

Thermal pre-warning and the TSD threshold have hysteresis of 20°C.

## **VS Under-Voltage Lockout (UVLO)**

If  $V_{VS}$  falls below the under-voltage lockout (UVLO) threshold, an internal timer starts. When a permanent UVLO delay time is reached, the power supply fail bit (PSF) in the output register is set and all outputs are disabled. Once  $V_{VS}$  exceeds the UVLO threshold and the PSF bit is cleared, the MP6527 resumes normal operation.

### **VCC UVLO**

The SPI interface does not function if  $V_{\text{CC}}$  is below the UVLO threshold. In this circumstance, all outputs turn off and clear the command input and status output registers.

Once  $V_{\text{CC}}$  exceeds the UVLO threshold, the UVLO resets and SRR is functional again.

### VS Over-Voltage Lockout (OVLO)

If  $V_{VS}$  exceeds the switch-off voltage ( $V_{OVOFF}$ ), all outputs are switched off by the set over-voltage lockout (OVLO) input bit (OVLO = 1, CH\_SEL = X) and the PSF error bit. The error is not latched, meaning if  $V_{VS}$  drops below the switch-on threshold voltage, the power stages restart and the error flags are reset.

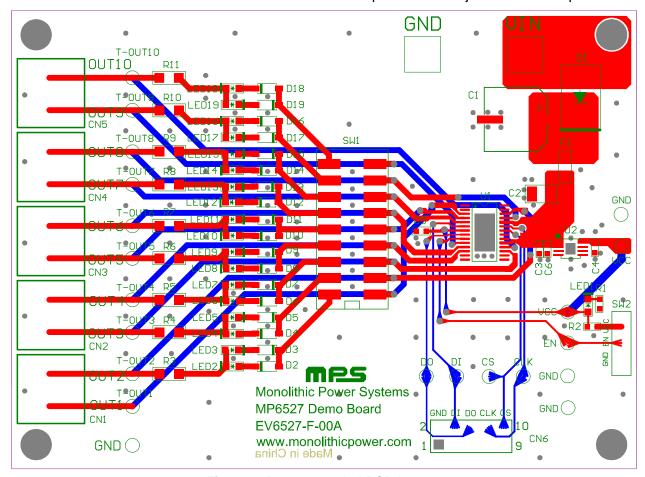

### APPLICATION INFORMATION

### **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation. For the best results, refer to Figure 6 and follow the guidelines below:

- 1. Place a bulk capacitor on the VIN pin to absorb the energy flowing from the motor or power supply. The capacitor should be sized according to the application requirements.

- 2. Place a supply bypass capacitor as close to the IC as possible. It is recommended to use a X5R or X7R dielectric capacitor.

- 3. Place as much copper on the long pads as possible.

- 4. Place multiple thermal vias inside the pad area to move heat to the copper layers. If the vias cannot be placed inside the pad area, place the vias just outside the pad area.

Figure 6: Recommended PCB Layout

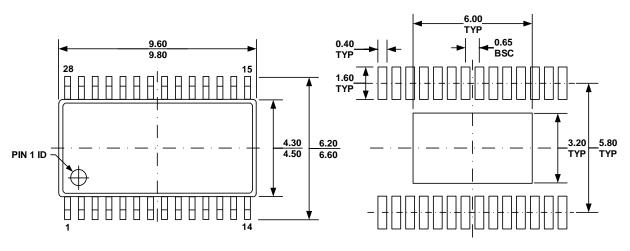

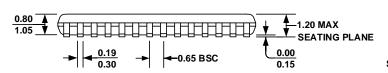

# **PACKAGE INFORMATION**

### TSSOP-28EP

**TOP VIEW**

RECOMMENDED LAND PATTERN

FRONT VIEW

SIDE VIEW

**BOTTOM VIEW**

**DETAIL "A"**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION, OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.1 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-153, VARIATION AET.

- 6) DRAWING IS NOT TO SCALE.

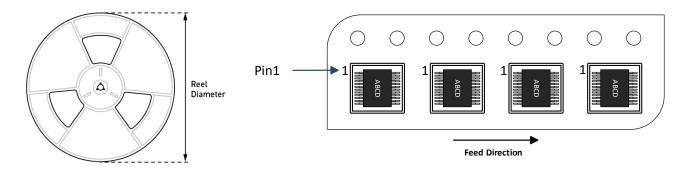

# **CARRIER INFORMATION**

| Part Number | Package     | Quantity/ | Quantity/ | Reel     | Carrier    | Carrier    |

|-------------|-------------|-----------|-----------|----------|------------|------------|

|             | Description | Reel      | Tube      | Diameter | Tape Width | Tape Pitch |

| MP6527GF-Z  | TSSOP-28EP  | 2500      | 50        | 13in     | 16mm       | 8mm        |

# **REVISION HISTORY**

| Revision # | Revision<br>Date | Description     | Pages Updated |

|------------|------------------|-----------------|---------------|

| 1.0        | 9/23/2021        | Initial Release | -             |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.